# LH1562

#### DESCRIPTION

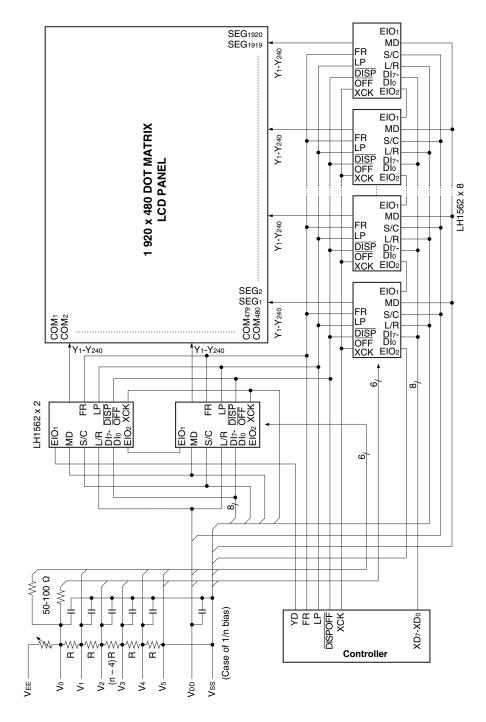

The LH1562 is a 240-output segment/common driver IC suitable for driving large/medium scale dot matrix LCD panels, and is used in personal computers/work stations. Through the use of SST (Super Slim TCP) technology, it is ideal for substantially decreasing the size of the frame section of the LCD module. The LH1562 is good both as a segment driver and a common driver, and it can create a low power consuming, highresolution LCD.

# FEATURES

- Number of LCD drive outputs : 240

- Supply voltage for LCD drive : +15.0 to +42.0 V

- Supply voltage for the logic system : +2.5 to +5.5 V

- Low power consumption

- Low output impedance

- Package : 269-pin TCP (Tape Carrier Package)

(Segment mode)

- Shift clock frequency

- -20 MHz (MAX.) : VDD =  $+5.0\pm0.5$  V

- 15 MHz (MAX.) : VDD = +3.0 to +4.5 V

- 12 MHz (MAX.) : VDD = +2.5 to +3.0 V

- Adopts a data bus system

- 4-bit/8-bit parallel input modes are selectable with a mode (MD) pin

- · Automatic transfer function of an enable signal

- Automatic counting function which, in the chip selection mode, causes the internal clock to be stopped by automatically counting 240 bits of input data

- Line latch circuits are reset when DISPOFF active

#### (Common mode)

- Shift clock frequency : 4 MHz (MAX.)

- Built-in 240-bit bi-directional shift register (divisible into 120 bits x 2)

# 240-output LCD Segment/Common Driver IC

- Available in a single mode (240-bit shift register) or in a dual mode (120-bit shift register x 2)

- ① Y1→Y240 Single mode

- ② Y240→Y1 Single mode

- ③ Y1→Y120, Y121→Y240 Dual mode

- ④ Y240→Y121, Y120→Y1 Dual mode

- The above 4 shift directions are pin-selectable

- Shift register circuits are reset when DISPOFF active

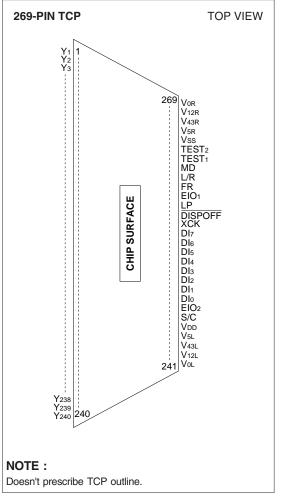

### **PIN CONNECTIONS**

In the absence of confirmation by device specification sheets, SHARP takes no responsibility for any defects that may occur in equipment using any SHARP devices shown in catalogs, data books, etc. Contact SHARP in order to obtain the latest device specification sheets before using any SHARP device.

#### **PIN DESCRIPTION**

| PIN NO.    | SYMBOL       | I/O | DESCRIPTION                                                                |  |  |  |  |  |

|------------|--------------|-----|----------------------------------------------------------------------------|--|--|--|--|--|

| 1 to 240   | Y1-Y240      | 0   | LCD drive output                                                           |  |  |  |  |  |

| 241, 269   | Vol, Vor     | -   | Power supply for LCD drive                                                 |  |  |  |  |  |

| 242, 268   | V12L, V12R   | -   | Power supply for LCD drive                                                 |  |  |  |  |  |

| 243, 267   | V43L, V43R   | _   | Power supply for LCD drive                                                 |  |  |  |  |  |

| 244, 266   | V5L, V5R     | -   | Power supply for LCD drive                                                 |  |  |  |  |  |

| 245        | Vdd          | -   | Power supply for logic system (+2.5 to +5.5 V)                             |  |  |  |  |  |

| 246        | S/C          | I   | Segment mode/common mode selection                                         |  |  |  |  |  |

| 247, 259   | EIO2, EIO1   | I/O | Input/output for chip selection at segment mode/                           |  |  |  |  |  |

| 247, 259   |              | 1/0 | Shift data input/output for shift register at common mode                  |  |  |  |  |  |

| 248 to 254 | DI0-DI6      | I   | Display data input at segment mode                                         |  |  |  |  |  |

| 255        | DI7          | I   | Display data input at segment mode/Dual mode data input at common mode     |  |  |  |  |  |

| 256        | XCK          | I   | Clock input for taking display data at segment mode                        |  |  |  |  |  |

| 257        | DISPOFF      | I   | Control input for output of non-select level                               |  |  |  |  |  |

| 258        | LP           | 1   | Latch pulse input for display data at segment mode/                        |  |  |  |  |  |

| 200        | LP           | I   | Shift clock input for shift register at common mode                        |  |  |  |  |  |

| 260        | FR           | I   | AC-converting signal input for LCD drive waveform                          |  |  |  |  |  |

| 061        | L/R          | 1   | Input for selecting the reading direction of display data at segment mode/ |  |  |  |  |  |

| 261        | L/R          | Į   | Input for selecting the shift direction of shift register at common mode   |  |  |  |  |  |

| 262        | MD           | I   | Mode selection input                                                       |  |  |  |  |  |

| 263, 264   | TEST1, TEST2 | I   | Test mode selection input                                                  |  |  |  |  |  |

| 265        | Vss          | _   | Ground (0 V)                                                               |  |  |  |  |  |

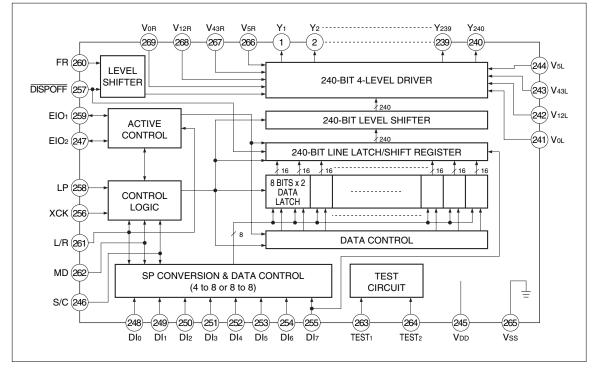

#### **BLOCK DIAGRAM**

# FUNCTIONAL OPERATIONS OF EACH BLOCK

| BLOCK              | FUNCTION                                                                                        |

|--------------------|-------------------------------------------------------------------------------------------------|

|                    | In case of segment mode, controls the selection or non-selection of the chip.                   |

|                    | Following an LP signal input, and after the chip selection signal is input, a selection         |

| Active Control     | signal is generated internally until 240 bits of data have been read in.                        |

| Active Control     | Once data input has been completed, a selection signal for cascade connection is                |

|                    | output, and the chip is non-selected.                                                           |

|                    | In case of common mode, controls the input/output data of bi-directional pins.                  |

| SP Conversion      | In case of segment mode, keeps input data which are 2 clocks of XCK at 4-bit parallel           |

| & Data Control     | input mode in latch circuit, or keeps input data which are 1 clock of XCK at 8-bit parallel     |

|                    | input mode in latch circuit; after that they are put on the internal data bus 8 bits at a time. |

|                    | In case of segment mode, selects the state of the data latch which reads in the data bus        |

| Data Latch Control | signals. The shift direction is controlled by the control logic. For every 16 bits of data      |

|                    | read in, the selection signal shifts one bit based on the state of the control circuit.         |

|                    | In case of segment mode, latches the data on the data bus. The latch state of each LCD          |

| Data Latch         | drive output pin is controlled by the control logic and the data latch control; 240 bits of     |

|                    | data are read in 30 sets of 8 bits.                                                             |

|                    | In case of segment mode, all 240 bits which have been read into the data latch are              |

| Line Latch/        | simultaneously latched at the falling edge of the LP signal, and are output to the level        |

| Shift Register     | shifter block. In case of common mode, shifts data from the data input pin at the falling       |

|                    | edge of the LP signal.                                                                          |

| Level Shifter      | The logic voltage signal is level-shifted to the LCD drive voltage level, and is output to      |

|                    | the driver block.                                                                               |

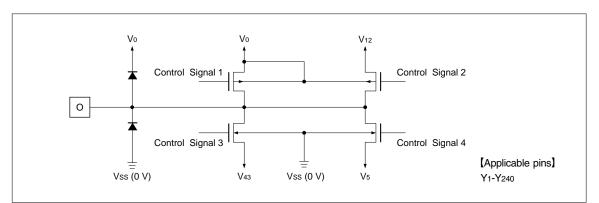

| 4-Level Driver     | Drives the LCD drive output pins from the line latch/shift register data, and selects one of    |

|                    | 4 levels (V0, V12, V43, or V5) based on the S/C, FR and DISPOFF signals.                        |

|                    | Controls the operation of each block. In case of segment mode, when an LP signal has            |

|                    | been input, all blocks are reset and the control logic waits for the selection signal output    |

| Control Logic      | from the active control block. Once the selection signal has been output, operation of the      |

|                    | data latch and data transmission is controlled, 240 bits of data are read in, and the chip      |

|                    | is non-selected. In case of common mode, controls the direction of data shift.                  |

| Test Circuit       | The circuit for testing. During normal operation, it isn't activated.                           |

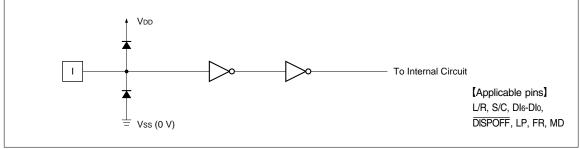

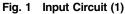

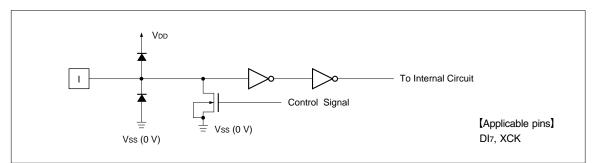

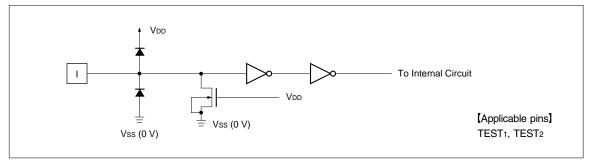

# **INPUT/OUTPUT CIRCUITS**

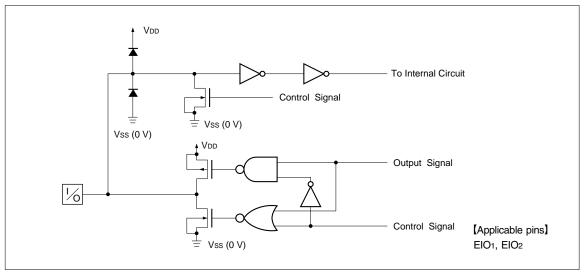

Fig. 2 Input Circuit (2)

Fig. 3 Input Circuit (3)

Fig. 4 Input/Output Circuit

Fig. 5 LCD Drive Output Circuit

# FUNCTIONAL DESCRIPTION

#### **Pin Functions**

(Segment mode)

| SYMBOL     | FUNCTION                                                                                          |

|------------|---------------------------------------------------------------------------------------------------|

| Vdd        | Logic system power supply pin, connected to +2.5 to +5.5 V.                                       |

| Vss        | Ground pin, connected to 0 V.                                                                     |

|            | Bias power supply pins for LCD drive voltage                                                      |

| Vol, Vor   | Normally use the bias voltages set by a resistor divider.                                         |

| V12L, V12R | • Ensure that voltages are set such that Vss $\leq$ V5 < V43 < V12 < V0.                          |

| V43L, V43R | • ViL and ViR (i = 0, 12, 43, 5) must connect to an external power supply, and supply regular     |

| V5L, V5R   | voltage which is assigned by specification for each power pin.                                    |

|            | Input pins for display data                                                                       |

|            | <ul> <li>In 4-bit parallel input mode, input data into the 4 pins, DI3-DI0.</li> </ul>            |

| DI7-DI0    | Connect DI7-DI4 to Vss or VDD.                                                                    |

| DI7-DI0    | <ul> <li>In 8-bit parallel input mode, input data into the 8 pins, DI7-DI0.</li> </ul>            |

|            | Refer to "RELATIONSHIP BETWEEN THE DISPLAY DATA AND LCD DRIVE OUTPUT                              |

|            | PINS" in Functional Operations.                                                                   |

| ХСК        | Clock input pin for taking display data                                                           |

| XUN        | <ul> <li>Data is read at the falling edge of the clock pulse.</li> </ul>                          |

| LP         | Latch pulse input pin for display data                                                            |

|            | <ul> <li>Data is latched at the falling edge of the clock pulse.</li> </ul>                       |

|            | Input pin for selecting the reading direction of display data                                     |

|            | • When set to Vss level "L", data is read sequentially from Y240 to Y1.                           |

| L/R        | • When set to VDD level "H", data is read sequentially from Y1 to Y240.                           |

|            | Refer to "RELATIONSHIP BETWEEN THE DISPLAY DATA AND LCD DRIVE OUTPUT                              |

|            | PINS" in Functional Operations.                                                                   |

|            | Control input pin for output of non-select level                                                  |

|            | • The input signal is level-shifted from logic voltage level to LCD drive voltage level, and      |

|            | controls the LCD drive circuit.                                                                   |

|            | • When set to Vss level "L", the LCD drive output pins (Y1-Y240) are set to level V5.             |

| DISPOFF    | • When set to "L", the contents of the line latch are reset, but the display data are read in the |

| DISPOFF    | data latch regardless of the condition of DISPOFF. When the DISPOFF function is canceled,         |

|            | the driver outputs non-select level (V12 or V43), then outputs the contents of the data latch at  |

|            | the next falling edge of the LP. At that time, if DISPOFF removal time does not correspond        |

|            | to what is shown in AC characteristics, it can not output the reading data correctly.             |

|            | • Table of truth values is shown in "TRUTH TABLE" in Functional Operations.                       |

| SYMBOL     | FUNCTION                                                                                                          |  |  |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|            | AC signal input pin for LCD drive waveform                                                                        |  |  |  |  |

|            | • The input signal is level-shifted from logic voltage level to LCD drive voltage level, and                      |  |  |  |  |

|            | controls the LCD drive circuit.                                                                                   |  |  |  |  |

| FR         | Normally it inputs a frame inversion signal.                                                                      |  |  |  |  |

|            | • The LCD drive output pins' output voltage levels can be set using the line latch output                         |  |  |  |  |

|            | signal and the FR signal.                                                                                         |  |  |  |  |

|            | • Table of truth values is shown in "TRUTH TABLE" in Functional Operations.                                       |  |  |  |  |

|            | Mode selection pin                                                                                                |  |  |  |  |

|            | • When set to Vss level "L", 8-bit parallel input mode is set.                                                    |  |  |  |  |

| MD         | • When set to VDD level "H", 4-bit parallel input mode is set.                                                    |  |  |  |  |

|            | Refer to "RELATIONSHIP BETWEEN THE DISPLAY DATA AND LCD DRIVE OUTPUT                                              |  |  |  |  |

|            | PINS" in Functional Operations.                                                                                   |  |  |  |  |

| S/C        | Segment mode/common mode selection pin                                                                            |  |  |  |  |

| 3/0        | When set to VDD level "H", segment mode is set.                                                                   |  |  |  |  |

|            | Input/output pins for chip selection                                                                              |  |  |  |  |

|            | • When L/R input is at Vss level "L", EIO1 is set for output, and EIO2 is set for input.                          |  |  |  |  |

|            | • When L/R input is at VDD level "H", EIO1 is set for input, and EIO2 is set for output.                          |  |  |  |  |

| EIO1, EIO2 | • During output, set to "H" while $LP \cdot \overline{XCK}$ is "H" and after 240 bits of data have been read, set |  |  |  |  |

|            | to "L" for one cycle (from falling edge to falling edge of XCK), after which it returns to "H".                   |  |  |  |  |

|            | • During input, the chip is selected while EI is set to "L" after the LP signal is input. The                     |  |  |  |  |

|            | chip is non-selected after 240 bits of data have been read.                                                       |  |  |  |  |

| TEST1      | Test mode selection pins                                                                                          |  |  |  |  |

| TEST2      | During normal operation, fix to Vss level "L".                                                                    |  |  |  |  |

|            | LCD drive output pins                                                                                             |  |  |  |  |

| Y1-Y240    | $\bullet$ Corresponding directly to each bit of the data latch, one level (V0, V12, V43, or V5) is                |  |  |  |  |

|            | selected and output.                                                                                              |  |  |  |  |

|            | • Table of truth values is shown in "TRUTH TABLE" in Functional Operations.                                       |  |  |  |  |

(Common mode)

| SYMBOL                                           | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vdd                                              | Logic system power supply pin, connected to +2.5 to +5.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Vss                                              | Ground pin, connected to 0 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V0L, V0R<br>V12L, V12R<br>V43L, V43R<br>V5L, V5R | <ul> <li>Bias power supply pins for LCD drive voltage</li> <li>Normally use the bias voltages set by a resistor divider.</li> <li>Ensure that voltages are set such that Vss ≤ V5 &lt; V43 &lt; V12 &lt; V0.</li> <li>ViL and ViR (i = 0, 12, 43, 5) must connect to an external power supply, and supply regular voltage which is assigned by specification for each power pin.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                          |

| EIO1                                             | <ul> <li>Shift data input/output pin for bi-directional shift register</li> <li>Output pin when L/R is at Vss level "L", input pin when L/R is at VDD level "H".</li> <li>When L/R = H, ElO1 is used as input pin, it will be pulled down.</li> <li>When L/R = L, ElO1 is used as output pin, it won't be pulled down.</li> <li>Refer to "RELATIONSHIP BETWEEN THE DISPLAY DATA AND LCD DRIVE OUTPUT PINS" in Functional Operations.</li> </ul>                                                                                                                                                                                                                                                                                                                                      |

| EIO2                                             | <ul> <li>Shift data input/output pin for bi-directional shift register</li> <li>Input pin when L/R is at Vss level "L", output pin when L/R is at Vbb level "H".</li> <li>When L/R = L, ElO2 is used as input pin, it will be pulled down.</li> <li>When L/R = H, ElO2 is used as output pin, it won't be pulled down.</li> <li>Refer to "RELATIONSHIP BETWEEN THE DISPLAY DATA AND LCD DRIVE OUTPUT PINS" in Functional Operations.</li> </ul>                                                                                                                                                                                                                                                                                                                                      |

| LP                                               | <ul><li>Shift clock pulse input pin for bi-directional shift register</li><li>Data is shifted at the falling edge of the clock pulse.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| L/R                                              | <ul> <li>Input pin for selecting the shift direction of bi-directional shift register</li> <li>Data is shifted from Y<sub>240</sub> to Y<sub>1</sub> when set to Vss level "L", and data is shifted from Y<sub>1</sub> to Y<sub>240</sub> when set to V<sub>DD</sub> level "H".</li> <li>Refer to "RELATIONSHIP BETWEEN THE DISPLAY DATA AND LCD DRIVE OUTPUT PINS" in Functional Operations.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                             |

| DISPOFF                                          | <ul> <li>Control input pin for output of non-select level</li> <li>The input signal is level-shifted from logic voltage level to LCD drive voltage level, and controls the LCD drive circuit.</li> <li>When set to Vss level "L", the LCD drive output pins (Y1-Y240) are set to level V5.</li> <li>When set to "L", the contents of the shift register are reset to not reading data. When the DISPOFF function is canceled, the driver outputs non-select level (V12 or V43), and the shift data is read at the next falling edge of the LP. At that time, if DISPOFF removal time does not correspond to what is shown in AC characteristics, the shift data is not read correctly.</li> <li>Table of truth values is shown in "TRUTH TABLE" in Functional Operations.</li> </ul> |

| SYMBOL  | FUNCTION                                                                                                                |

|---------|-------------------------------------------------------------------------------------------------------------------------|

|         | AC signal input pin for LCD drive waveform                                                                              |

|         | • The input signal is level-shifted from logic voltage level to LCD drive voltage level, and                            |

|         | controls the LCD drive circuit.                                                                                         |

| FR      | Normally it inputs a frame inversion signal.                                                                            |

|         | • The LCD drive output pins' output voltage levels can be set using the shift register output signal and the FR signal. |

|         | • Table of truth values is shown in "TRUTH TABLE" in Functional Operations.                                             |

|         | Mode selection pin                                                                                                      |

|         | • When set to Vss level "L", single mode operation is selected; when set to Vbb level "H",                              |

| MD      | dual mode operation is selected.                                                                                        |

|         | Refer to "RELATIONSHIP BETWEEN THE DISPLAY DATA AND LCD DRIVE OUTPUT                                                    |

|         | PINS" in Functional Operations.                                                                                         |

|         | Dual mode data input pin                                                                                                |

|         | • According to the data shift direction of the data shift register, data can be input starting                          |

|         | from the 121st bit.                                                                                                     |

| DI7     | When the chip is used in dual mode, DI7 will be pulled down.                                                            |

|         | When the chip is used in single mode, DI7 won't be pulled down.                                                         |

|         | Refer to "RELATIONSHIP BETWEEN THE DISPLAY DATA AND LCD DRIVE OUTPUT                                                    |

|         | PINS" in Functional Operations.                                                                                         |

| S/C     | Segment mode/common mode selection pin                                                                                  |

| 0,0     | When set to Vss level "L", common mode is set.                                                                          |

| DI6-DI0 | Not used                                                                                                                |

| BI0 BI0 | Connect DI6-DI0 to Vss or VDD, avoiding floating.                                                                       |

| хск     | Not used                                                                                                                |

|         | XCK is pulled down in common mode, so connect to Vss or open.                                                           |

| TEST1   | Test mode selection pins                                                                                                |

| TEST2   | During normal operation, fix to Vss level "L".                                                                          |

|         | LCD drive output pins                                                                                                   |

| Y1-Y240 | • Corresponding directly to each bit of the shift register, one level (V0, V12, V43, or V5) is                          |

|         | selected and output.                                                                                                    |

|         | • Table of truth values is shown in "TRUTH TABLE" in Functional Operations.                                             |

# Functional Operations TRUTH TABLE

#### (Segment Mode)

| FR | LATCH DATA | DISPOFF | LCD DRIVE OUTPUT VOLTAGE LEVEL (Y1-Y240) |

|----|------------|---------|------------------------------------------|

| L  | L          | Н       | V43                                      |

| L  | Н          | Н       | V5                                       |

| Н  | L          | Н       | V12                                      |

| Н  | Н          | Н       | Vo                                       |

| Х  | Х          | L       | V5                                       |

#### (Common Mode)

| FR | LATCH DATA | DISPOFF | LCD DRIVE OUTPUT VOLTAGE LEVEL (Y1-Y240) |

|----|------------|---------|------------------------------------------|

| L  | L          | Н       | V43                                      |

| L  | Н          | Н       | Vo                                       |

| Н  | L          | Н       | V12                                      |

| Н  | Н          | Н       | V5                                       |

| Х  | Х          | L       | V5                                       |

#### NOTES :

+ Vss  $\leq$  V5 < V43 < V12 < V0, L : Vss (0 V), H : Vdd (+2.5 to +5.5 V), X : Don't care

"Don't care" should be fixed to "H" or "L", avoiding floating.

There are two kinds of power supply (logic level voltage and LCD drive voltage) for the LCD driver.

Supply regular voltage which is assigned by specification for each power pin.

#### RELATIONSHIP BETWEEN THE DISPLAY DATA AND LCD DRIVE OUTPUT PINS

#### (Segment Mode )

(a) 4-bit Parallel Input Mode

| МБ | MD L/R | EIO1       | EIO <sub>2</sub> | DATA     | NUMBER OF CLOCKS |          |      |         |         |         |            |

|----|--------|------------|------------------|----------|------------------|----------|------|---------|---------|---------|------------|

|    | EIU1   | EIO2       | INPUT            | 60 CLOCK | 59 CLOCK         | 58 CLOCK |      | 3 CLOCK | 2 CLOCK | 1 CLOCK |            |

|    |        |            |                  | Dlo      | Y1               | Y5       | Y9   |         | Y229    | Y233    | Y237       |

| Н  |        | Output     | Input            | DI1      | Y2               | Y6       | Y10  |         | Y230    | Y234    | Y238       |

|    |        |            |                  | DI2      | Y3               | Y7       | Y11  |         | Y231    | Y235    | Y239       |

|    |        |            |                  | DIз      | Y4               | Y8       | Y12  |         | Y232    | Y236    | Y240       |

|    |        | lawst      |                  | Dlo      | Y240             | Y236     | Y232 |         | Y12     | Y8      | Y4         |

| Н  |        |            |                  | DI1      | Y239             | Y235     | Y231 |         | Y11     | Y7      | Y3         |

| нн | Input  | put Output | DI2              | Y238     | Y234             | Y230     |      | Y10     | Y6      | Y2      |            |

|    |        |            |                  | DIз      | Y237             | Y233     | Y229 |         | Y9      | Y5      | <b>Y</b> 1 |

#### (b) 8-bit Parallel Input Mode

| MD | L/R | EIO1   | EIO <sub>2</sub> | DATA  |          |          | NUMB     | ER OF CI | LOCKS   |         |         |

|----|-----|--------|------------------|-------|----------|----------|----------|----------|---------|---------|---------|

|    |     | EIU1   |                  | INPUT | 30 CLOCK | 29 CLOCK | 28 CLOCK |          | 3 CLOCK | 2 CLOCK | 1 CLOCK |

|    |     |        |                  | Dlo   | Y1       | Y9       | Y17      |          | Y217    | Y225    | Y233    |

|    |     |        | DI1              | Y2    | Y10      | Y18      |          | Y218     | Y226    | Y234    |         |

|    |     |        |                  | Dl2   | Y3       | Y11      | Y19      |          | Y219    | Y227    | Y235    |

|    |     | Output | Innut            | DIз   | Y4       | Y12      | Y20      |          | Y220    | Y228    | Y236    |

|    | L   | Output | Input            | DI4   | Y5       | Y13      | Y21      |          | Y221    | Y229    | Y237    |

|    |     |        |                  | DI5   | Y6       | Y14      | Y22      |          | Y222    | Y230    | Y238    |

|    |     |        |                  | DI6   | Y7       | Y15      | Y23      |          | Y223    | Y231    | Y239    |

|    |     |        |                  | DI7   | Y8       | Y16      | Y24      |          | Y224    | Y232    | Y240    |

|    |     | Input  |                  | Dlo   | Y240     | Y232     | Y224     |          | Y24     | Y16     | Y8      |

|    |     |        | Output           | DI1   | Y239     | Y231     | Y223     |          | Y23     | Y15     | Y7      |

|    |     |        |                  | Dl2   | Y238     | Y230     | Y222     |          | Y22     | Y14     | Y6      |

|    | н   |        |                  | DIз   | Y237     | Y229     | Y221     |          | Y21     | Y13     | Y5      |

|    |     |        |                  | DI4   | Y236     | Y228     | Y220     |          | Y20     | Y12     | Y4      |

|    |     |        |                  | DI5   | Y235     | Y227     | Y219     |          | Y19     | Y11     | Y3      |

|    |     |        |                  | DI6   | Y234     | Y226     | Y218     |          | Y18     | Y10     | Y2      |

|    |     |        |                  | DI7   | Y233     | Y225     | Y217     |          | Y17     | Y9      | Y1      |

#### (Common Mode)

| MD       | L/R | DATA TRANSFER DIRECTION       | EIO1   | EIO <sub>2</sub> | DI7   |  |

|----------|-----|-------------------------------|--------|------------------|-------|--|

| L        | L   | $Y_{240} \rightarrow Y_1$     | Output | Input            | Х     |  |

| (Single) | Н   | $Y_1 \rightarrow Y_{240}$     | Input  | Output           | Х     |  |

|          | L   | Y240 → Y121                   | Output | Input            | Input |  |

| н        |     | $Y_{120} \rightarrow Y_1$     | Output |                  |       |  |

| (Dual)   | Ц   | $Y_1 \rightarrow Y_{120}$     | Input  | Quitout          | Input |  |

|          | н   | $Y_{121} \rightarrow Y_{240}$ | Input  | Output           | Input |  |

#### NOTES :

• L : Vss (0 V), H : VDD (+2.5 to +5.5 V), X : Don't care

• "Don't care" should be fixed to "H" or "L", avoiding floating.

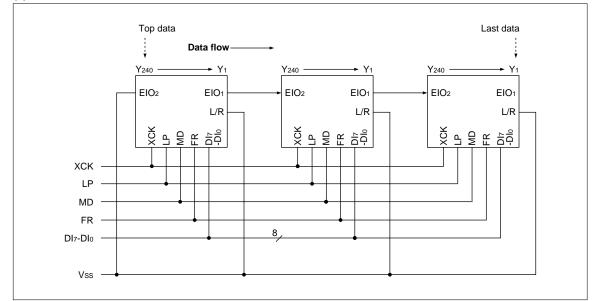

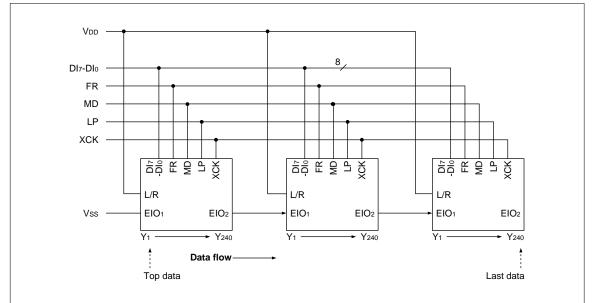

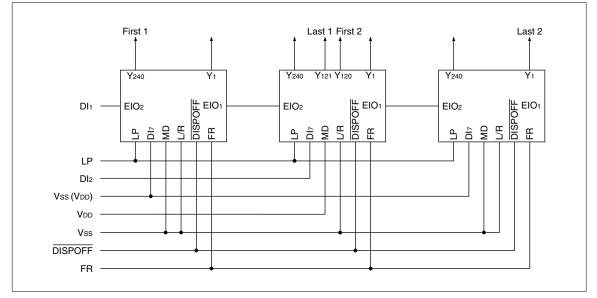

#### CONNECTION EXAMPLES OF PLURAL SEGMENT DRIVERS

(a) When L/R = "L"

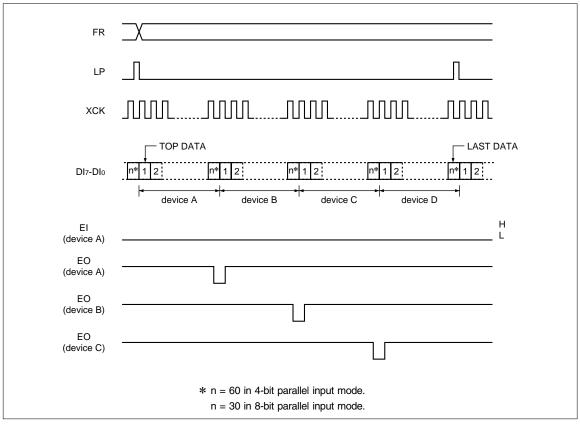

#### TIMING CHART OF 4-DEVICE CASCADE CONNECTION OF SEGMENT DRIVERS

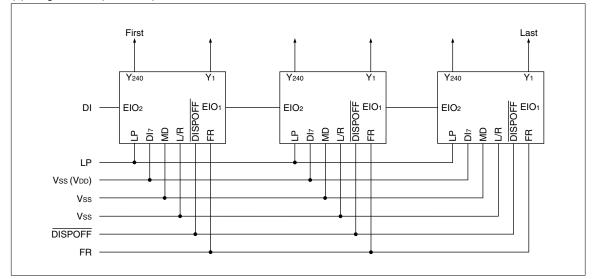

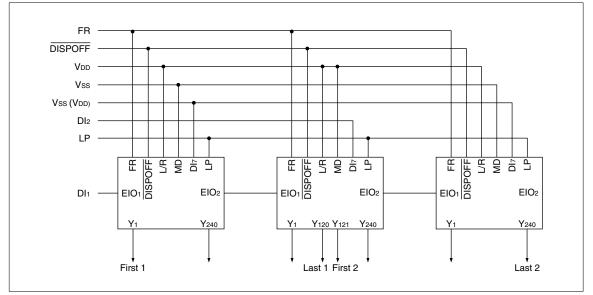

#### CONNECTION EXAMPLES FOR PLURAL COMMON DRIVERS

(a) Single Mode (L/R = "L")

#### (b) Single Mode (L/R = "H")

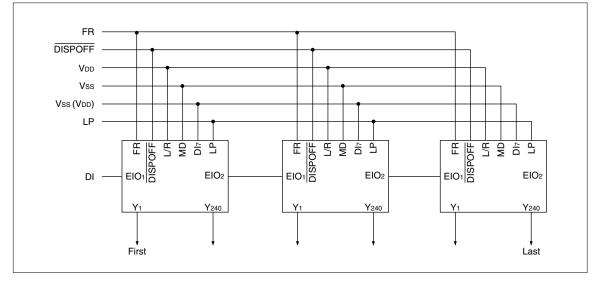

#### (c) Dual Mode (L/R = "L")

#### (d) Dual Mode (L/R = "H")

#### PRECAUTIONS

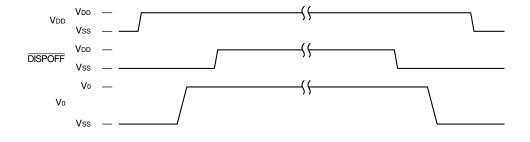

# Precautions when connecting or disconnecting the power supply

This IC has a high-voltage LCD driver, so it may be permanently damaged by a high current which may flow if voltage is supplied to the LCD drive power supply while the logic system power supply is floating. The details are as follows.

- When connecting the power supply, connect the LCD drive power after connecting the logic system power. Furthermore, when disconnecting the power, disconnect the logic system power after disconnecting the LCD drive power.

- It is advisable to connect the serial resistor (50 to 100 Ω) or fuse to the LCD drive power Vo of the system as a current limiter. Set up a suitable value of the resistor in consideration of the display grade.

And when connecting the logic power supply, the logic condition of this IC inside is insecure. Therefore connect the LCD drive power supply after resetting logic condition of this IC inside on DISPOFF function. After that, cancel the DISPOFF function after the LCD drive power supply has become stable. Furthermore, when disconnecting the power, set the LCD drive output pins to level V<sub>5</sub> on DISPOFF function. Then disconnect the logic system power after disconnecting the LCD drive power.

When connecting the power supply, follow the recommended sequence shown here.

# **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER           | SYMBOL | APPLICABLE PINS            | RATING            | UNIT | NOTE |

|---------------------|--------|----------------------------|-------------------|------|------|

| Supply voltage (1)  | Vdd    | Vdd                        | -0.3 to +7.0      | V    |      |

|                     | Vo     | Vol, Vor                   | -0.3 to +45.0     | V    |      |

| Supply voltage (2)  | V12    | V12L, V12R                 | -0.3 to V0 + 0.3  | V    |      |

| Supply voltage (2)  | V43    | V43L, V43R                 | -0.3 to V0 + 0.3  | V    | 1.0  |

|                     | V5     | V5L, V5R                   | -0.3 to V0 + 0.3  | V    | 1, 2 |

|                     |        | DI7-DI0, XCK, LP, L/R, FR, |                   |      |      |

| Input voltage       | Vi     | MD, S/C, EIO1, EIO2,       | -0.3 to VDD + 0.3 | V    |      |

|                     |        | DISPOFF, TEST1, TEST2      |                   |      |      |

| Storage temperature | Tstg   |                            | -45 to +125       | °C   |      |

#### NOTES :

1. TA = +25 °C

2. The maximum applicable voltage on any pin with respect to Vss (0 V).

# **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER             | SYMBOL | APPLICABLE PINS | MIN.  | TYP. | MAX.  | UNIT | NOTE |

|-----------------------|--------|-----------------|-------|------|-------|------|------|

| Supply voltage (1)    | Vdd    | VDD             | +2.5  |      | +5.5  | V    | 12   |

| Supply voltage (2)    | Vo     | Vol, Vor        | +15.0 |      | +42.0 | V    | 1, 2 |

| Operating temperature | TOPR   |                 | -20   |      | +85   | °C   |      |

#### NOTES :

1. The applicable voltage on any pin with respect to Vss (0 V).

2. Ensure that voltages are set such that Vss  $\leq$  V5 < V43 < V12 < V0.

# **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics**

| (Segment Mode) | (Vss = V | $V_5 = 0 V, V_{DD} = -$ | +2.5 to +5.5 V, Vo = +1 | 5.0 to + | 42.0 V, | TOPR = | -20 to | +85 °C) |

|----------------|----------|-------------------------|-------------------------|----------|---------|--------|--------|---------|

|                |          |                         |                         |          |         |        |        |         |

| PARAMETER                             | SYMBOL | CON                            | DITIONS   | APPLICABLE PINS                              | MIN.      | TYP. | MAX.   | UNIT | NOTE |

|---------------------------------------|--------|--------------------------------|-----------|----------------------------------------------|-----------|------|--------|------|------|

| Input "Low" voltage                   | Vı∟    |                                |           | DI7-DI0, XCK, LP, L/R,                       |           |      | 0.2Vdd | V    |      |

| Input "High" voltage                  | Vін    |                                |           | FR, MD, S/C, EIO1,<br>EIO2, DISPOFF          | 0.8Vdd    |      |        | V    |      |

| Output "Low" voltage                  | Vol    | IOL = ·                        | +0.4 mA   |                                              |           |      | +0.4   | V    |      |

| Output "High" voltage                 | Vон    | Юн = -                         | –0.4 mA   | EIO1, EIO2                                   | Vdd - 0.4 |      |        | V    |      |

| Input lookago ourront                 | ILIL   | Vi :                           | = Vss     | DI7-DI0, XCK, LP, L/R,<br>FR, MD, S/C, EIO1, |           |      | -10.0  | μA   |      |

| Input leakage current                 | Іцн    | VI =                           | = Vdd     | $EIO_2, \overline{DISPOFF}$                  |           |      | +10.0  | μA   |      |

|                                       | Ron    |                                | V0 = 40 V |                                              |           | 1.0  | 1.5    |      |      |

| Output resistance                     |        | $ \Delta V_{ON} $ $V_0 = 30 V$ | Y1-Y240   |                                              | 1.5       | 2.0  | kΩ     |      |      |

|                                       |        | = 0.5 V                        | V0 = 20 V |                                              |           | 2.0  | 2.5    |      |      |

| Standby current                       | ISTB   |                                |           | Vss                                          |           |      | 75.0   | μA   | 1    |

| Supply current (1)<br>(Non-selection) | IDD1   |                                |           | VDD                                          |           |      | 2.0    | mA   | 2    |

| Supply current (2)<br>(Selection)     | IDD2   |                                |           | VDD                                          |           |      | 12.0   | mA   | 3    |

| Supply current (3)                    | lo     |                                |           | Vol, Vor                                     |           |      | 1.5    | mA   | 4    |

#### NOTES :

- 1. VDD = +5.0 V, V0 = +42.0 V, V1 = VSS.

- 2. VDD = +5.0 V, Vo = +42.0 V, fxck = 20 MHz, no-load, EI = VDD.

The input data is turned over by data taking clock (4-bit parallel input mode).

3. VDD = +5.0 V, Vo = +42.0 V, fxck = 20 MHz, no-load, EI = Vss.

The input data is turned over by data taking clock (4-bit parallel input mode).

4. VDD = +5.0 V, V0 = +42.0 V, fxck = 20 MHz, fLP = 41.6 kHz, fFR = 80 Hz, no-load.

The input data is turned over by data taking clock (4-bit parallel input mode).

| (Common Mode) (Vss = V5 = 0 V, VDD = +2.5 to +5.5 V, V0 = +15.0 to +42.0 V, TOPR = -20 to +85 °C) |        |                              |                                                               |           |      |        |      |      |  |

|---------------------------------------------------------------------------------------------------|--------|------------------------------|---------------------------------------------------------------|-----------|------|--------|------|------|--|

| PARAMETER                                                                                         | SYMBOL | CONDITIONS                   | APPLICABLE PINS                                               | MIN.      | TYP. | MAX.   | UNIT | NOTE |  |

| Input "Low" voltage                                                                               | Vi∟    |                              | DI7-DI0, XCK, LP, L/R,                                        |           |      | 0.2Vdd | V    |      |  |

| Input "High" voltage                                                                              | Vін    |                              | FR, MD, S/C, EIO1,<br>EIO2, DISPOFF                           | 0.8VDD    |      |        | V    |      |  |

| Output "Low" voltage                                                                              | Vol    | IoL = +0.4 mA                |                                                               |           |      | +0.4   | V    |      |  |

| Output "High" voltage                                                                             | Vон    | Iон = -0.4 mA                | EIO1, EIO2                                                    | Vdd - 0.4 |      |        | V    |      |  |

| Input leakage current                                                                             | ILIL   | VI = VSS                     | DI7-DI0, XCK, LP, L/R,<br>FR, MD, S/C, EIO1,<br>EIO2, DISPOFF |           |      | -10.0  | μA   |      |  |

|                                                                                                   | Іцн    | VI = VDD                     | DI6-DI0, LP, L/R, FR,<br>MD, S/C, DISPOFF                     |           |      | +10.0  | μA   |      |  |

| Input pull-down<br>current                                                                        | IPD    | VI = VDD                     | DI7, XCK, EIO1, EIO2                                          |           |      | 100.0  | μA   |      |  |

|                                                                                                   |        | V0 = 40 V                    |                                                               |           | 1.0  | 1.5    |      |      |  |

| Output resistance                                                                                 | Ron    | $\Delta V_{ON}$ $V_0 = 30 V$ | Y1-Y240                                                       |           | 1.5  | 2.0    | kΩ   |      |  |

|                                                                                                   |        | = 0.5 V Vo = 20 V            |                                                               |           | 2.0  | 2.5    |      |      |  |

| Standby current                                                                                   | Istb   |                              | Vss                                                           |           |      | 75.0   | μA   | 1    |  |

| Supply current (1)                                                                                | IDD    |                              | Vdd                                                           |           |      | 120.0  | μA   | 2    |  |

| Supply current (2)                                                                                | lo     |                              | Vol, Vor                                                      |           |      | 240.0  | μA   | 2    |  |

#### NOTES :

1. VDD = +5.0 V, V0 = +42.0 V, VI = VSS

2. VDD = +5.0 V, Vo = +42.0 V, fLP = 41.6 kHz, fFR = 80 Hz, 1/480 duty operation, no-load.

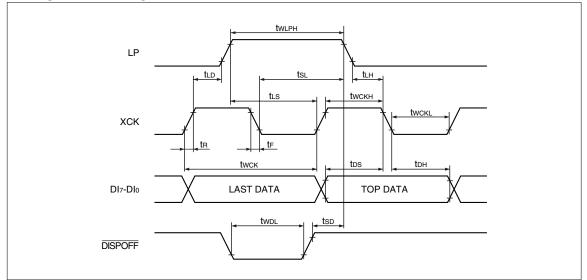

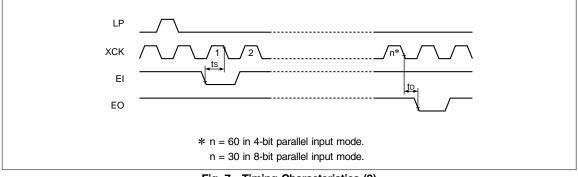

# **AC Characteristics**

| PARAMETER                                 | SYMBOL     | CONDITIONS     | MIN. | TYP. | MAX. | UNIT | NOTE |

|-------------------------------------------|------------|----------------|------|------|------|------|------|

| Shift clock period                        | twcĸ       | tR, tF ≤ 10 ns | 50   |      |      | ns   | 1    |

| Shift clock "H" pulse width               | twcкн      |                | 15   |      |      | ns   |      |

| Shift clock "L" pulse width               | tWCKL      |                | 15   |      |      | ns   |      |

| Data setup time                           | tDS        |                | 10   |      |      | ns   |      |

| Data hold time                            | tDH        |                | 12   |      |      | ns   |      |

| Latch pulse "H" pulse width               | tWLPH      |                | 15   |      |      | ns   |      |

| Shift clock rise to latch pulse rise time | tLD        |                | 0    |      |      | ns   |      |

| Shift clock fall to latch pulse fall time | tsL        |                | 30   |      |      | ns   |      |

| Latch pulse rise to shift clock rise time | tLS        |                | 25   |      |      | ns   |      |

| Latch pulse fall to shift clock fall time | tlн        |                | 25   |      |      | ns   |      |

| Enable setup time                         | ts         |                | 10   |      |      | ns   |      |

| Input signal rise time                    | tR         |                |      |      | 50   | ns   | 2    |

| Input signal fall time                    | tF         |                |      |      | 50   | ns   | 2    |

| DISPOFF removal time                      | tSD        |                | 100  |      |      | ns   |      |

| DISPOFF "L" pulse width                   | tWDL       |                | 1.2  |      |      | μs   |      |

| Output delay time (1)                     | tD         | C∟ = 15 pF     |      |      | 30   | ns   |      |

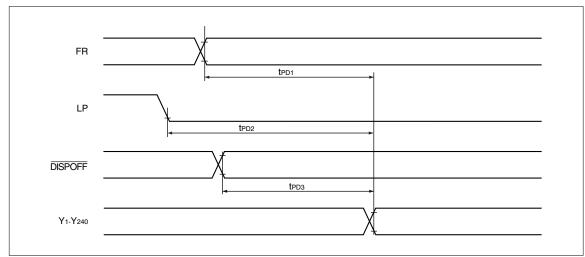

| Output delay time (2)                     | tPD1, tPD2 | C∟ = 15 pF     |      |      | 1.2  | μs   |      |

| Output delay time (3)                     | tPD3       | CL = 15 pF     |      |      | 1.2  | μs   |      |

#### NOTES :

1. Takes the cascade connection into consideration.

2. (twck – twckh – twckL)/2 is maximum in the case of high speed operation.

| PARAMETER                                 | SYMBOL     | CONDITIONS          | MIN. | TYP. | MAX. | UNIT | NOTE |

|-------------------------------------------|------------|---------------------|------|------|------|------|------|

| Shift clock period                        | twcĸ       | tR, tF $\leq$ 10 ns | 66   |      |      | ns   | 1    |

| Shift clock "H" pulse width               | twckh      |                     | 23   |      |      | ns   |      |

| Shift clock "L" pulse width               | twckl      |                     | 23   |      |      | ns   |      |

| Data setup time                           | tDS        |                     | 15   |      |      | ns   |      |

| Data hold time                            | tDH        |                     | 23   |      |      | ns   |      |

| Latch pulse "H" pulse width               | twlph      |                     | 30   |      |      | ns   |      |

| Shift clock rise to latch pulse rise time | tLD        |                     | 0    |      |      | ns   |      |

| Shift clock fall to latch pulse fall time | tsL        |                     | 50   |      |      | ns   |      |

| Latch pulse rise to shift clock rise time | tLS        |                     | 30   |      |      | ns   |      |

| Latch pulse fall to shift clock fall time | tLH        |                     | 30   |      |      | ns   |      |

| Enable setup time                         | ts         |                     | 15   |      |      | ns   |      |

| Input signal rise time                    | tR         |                     |      |      | 50   | ns   | 2    |

| Input signal fall time                    | tF         |                     |      |      | 50   | ns   | 2    |

| DISPOFF removal time                      | tSD        |                     | 100  |      |      | ns   |      |

| DISPOFF "L" pulse width                   | tWDL       |                     | 1.2  |      |      | μs   |      |

| Output delay time (1)                     | tD         | C∟ = 15 pF          |      |      | 41   | ns   |      |

| Output delay time (2)                     | tPD1, tPD2 | C∟ = 15 pF          |      |      | 1.2  | μs   |      |

| Output delay time (3)                     | tPD3       | C∟ = 15 pF          |      |      | 1.2  | μs   |      |

#### NOTES :

1. Takes the cascade connection into consideration.

2. (twck - twckH - twckL)/2 is maximum in the case of high speed operation.

| PARAMETER                                 | SYMBOL     | CONDITIONS          | MIN. | TYP. | MAX. | UNIT | NOTE |

|-------------------------------------------|------------|---------------------|------|------|------|------|------|

| Shift clock period                        | twcĸ       | tR, tF $\leq$ 10 ns | 82   |      |      | ns   | 1    |

| Shift clock "H" pulse width               | twcкн      |                     | 28   |      |      | ns   |      |

| Shift clock "L" pulse width               | twckl      |                     | 28   |      |      | ns   |      |

| Data setup time                           | tDS        |                     | 20   |      |      | ns   |      |

| Data hold time                            | tDH        |                     | 23   |      |      | ns   |      |

| Latch pulse "H" pulse width               | tWLPH      |                     | 30   |      |      | ns   |      |

| Shift clock rise to latch pulse rise time | tLD        |                     | 0    |      |      | ns   |      |

| Shift clock fall to latch pulse fall time | tsL        |                     | 65   |      |      | ns   |      |

| Latch pulse rise to shift clock rise time | tLS        |                     | 30   |      |      | ns   |      |

| Latch pulse fall to shift clock fall time | tlн        |                     | 30   |      |      | ns   |      |

| Enable setup time                         | ts         |                     | 15   |      |      | ns   |      |

| Input signal rise time                    | tR         |                     |      |      | 50   | ns   | 2    |

| Input signal fall time                    | tF         |                     |      |      | 50   | ns   | 2    |

| DISPOFF removal time                      | tSD        |                     | 100  |      |      | ns   |      |

| DISPOFF "L" pulse width                   | tWDL       |                     | 1.2  |      |      | μs   |      |

| Output delay time (1)                     | tD         | C∟ = 15 pF          |      |      | 57   | ns   |      |

| Output delay time (2)                     | tPD1, tPD2 | C∟ = 15 pF          |      |      | 1.2  | μs   |      |

| Output delay time (3)                     | tPD3       | C∟ = 15 pF          |      |      | 1.2  | μs   |      |

#### NOTES :

1. Takes the cascade connection into consideration.

2. (twck - twckh - twckL)/2 is maximum in the case of high speed operation.

# **Timing Chart of Segment Mode**

Fig. 6 Timing Characteristics (1)

Fig. 7 Timing Characteristics (2)

Fig. 8 Timing Characteristics (3)

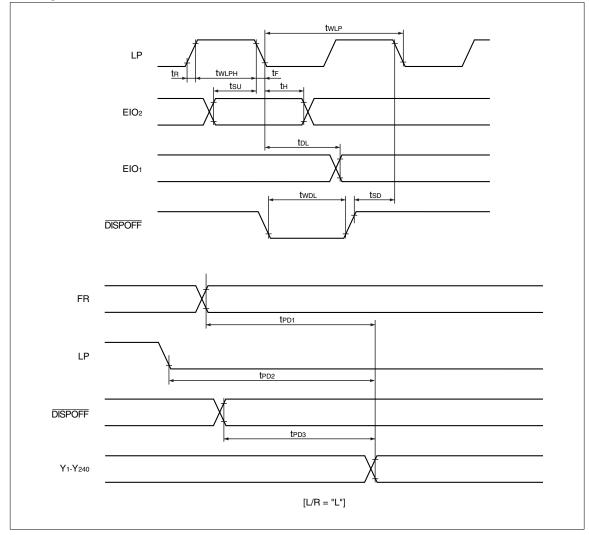

| (Common Mode) (Vss = V5 = 0 V, VDD = +2.5 to +5.5 V, V0 = +15.0 to +42.0 V, TOPR = -20 to +85 °C |            |                        |      |      |      |      |  |  |  |  |

|--------------------------------------------------------------------------------------------------|------------|------------------------|------|------|------|------|--|--|--|--|

| PARAMETER                                                                                        | SYMBOL     | CONDITIONS             | MIN. | TYP. | MAX. | UNIT |  |  |  |  |

| Shift clock period                                                                               | twLP       | tR, tF ≤ 20 ns         | 250  |      |      | ns   |  |  |  |  |

| Shift clock "H" pulse width                                                                      | twlph      | $VDD = +5.0 \pm 0.5 V$ | 15   |      |      | ns   |  |  |  |  |

|                                                                                                  | IVVLPH     | VDD = +2.5 to +4.5 V   | 30   |      |      | ns   |  |  |  |  |

| Data setup time                                                                                  | tsu        |                        | 30   |      |      | ns   |  |  |  |  |

| Data hold time                                                                                   | tн         |                        | 50   |      |      | ns   |  |  |  |  |

| Input signal rise time                                                                           | tR         |                        |      |      | 50   | ns   |  |  |  |  |

| Input signal fall time                                                                           | tF         |                        |      |      | 50   | ns   |  |  |  |  |

| DISPOFF removal time                                                                             | tSD        |                        | 100  |      |      | ns   |  |  |  |  |

| DISPOFF "L" pulse width                                                                          | tWDL       |                        | 1.2  |      |      | μs   |  |  |  |  |

| Output delay time (1)                                                                            | tDL        | CL = 15 pF             |      |      | 200  | ns   |  |  |  |  |

| Output delay time (2)                                                                            | tPD1, tPD2 | CL = 15 pF             |      |      | 1.2  | μs   |  |  |  |  |

| Output delay time (3)                                                                            | tPD3       | CL = 15 pF             |      |      | 1.2  | μs   |  |  |  |  |

# **Timing Chart of Common Mode**

# SYSTEM CONFIGURATION EXAMPLE

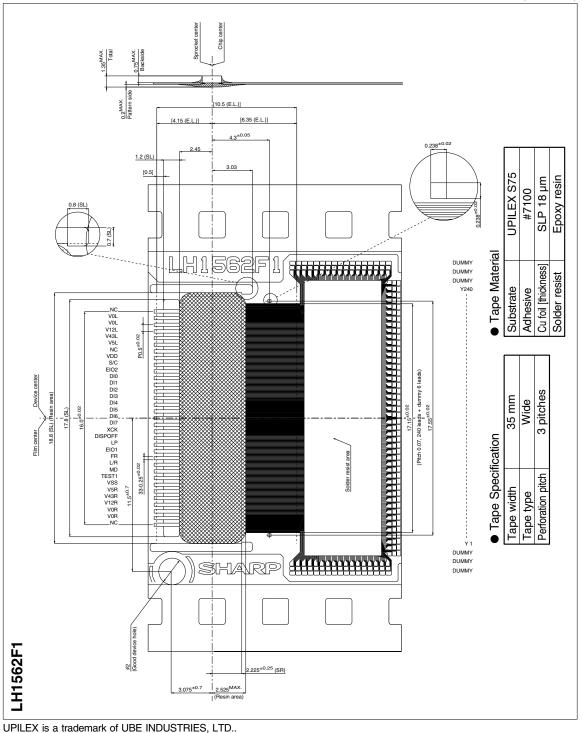

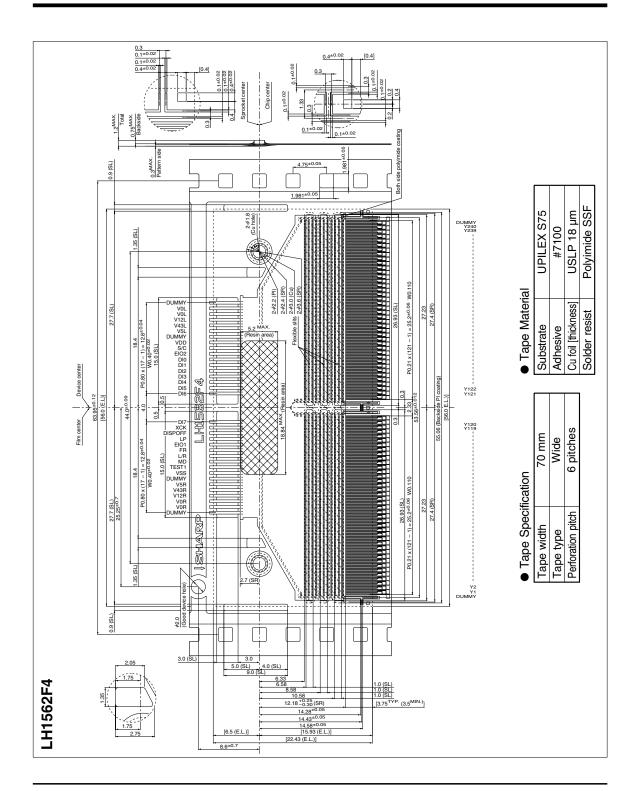

#### PACKAGES

(Unit : mm)